| Printed Pages-3       |             |      |      |      |      |    |      |    | EE  | 10 | 02  |

|-----------------------|-------------|------|------|------|------|----|------|----|-----|----|-----|

| (Following Paper ID a | nd Roll No. | to l | be f | ille | d in | yo | ur A | ns | wer | Bo | ok) |

| PAPER ID : 0323       | Roll No.    | 24   | 4    |      |      |    |      |    |     |    |     |

## B. Tech.

## (SEM. III) ODD SEMESTER THEORY EXAMINATION 2010-11

## DIGITAL ELECTRONICS

Time : 3 Hours

Total Marks : 100

FECSOS

- Note: (1) Attempt all questions.

- (2) All questions carry equal marks.

- 1. Attempt any four of the following :

- (a) Convert the following decimal numbers to their binary equivalents :

- (i) (83)<sub>10</sub>

- (ii) (79.515)<sub>10</sub>

- (iii) (109.125)<sub>10</sub>

- (b) Perform the following operations by using 2's complement method :

- (i) 46 23

- (ii) 21 42

- (c) Perform the following subtractions of BCD numbers using 9's complement :

- (i) 68 24

- (ii) 24-29

- (d) Explain with examples, how Hamming code is useful for detecting and correcting errors in digital data transmission.

EEC302/VEQ-15048

[Turn Over

(e) Convert the following Boolean function into standard SOP and express it in terms of minterms :

$Y(A, B, C) = AB + AC + B\overline{C}.$

- (f) Minimize the following expression using K-map :  $Y(A, B, C) = \Sigma(1, 2, 6, 7) + d(0, 5).$

- 2. Attempt any four of the following :

- (a) Design a 8-bit BCD adder.

- (b) Implement a 16:1 Multiplexer using 4:1 Multiplexers.

- (c) Design a BCD to Excess-3 Code Converter.

- (d) Design a full adder using NAND gates only.

- (e) Design a combinational logic circuit with three input variables that will produce logic 1 output when more than one input variables are logic 1.

- (f) Design a 2-bit comparator using logic gates.

- 3. Attempt any two of the following :

- (a) What is race-around condition ? How does it get eliminated in Master-slave J-K flip flop ? Explain.

- (b) Design and implement a Mod-6 synchronous counter using D-flip flop.

- (c) Design an asynchronous sequential circuit with two inputs  $I_1$  and  $I_2$ , and one output, Z. Initially, both inputs are equal to 0. When  $I_1$  changes from 0 to 1, Z becomes 1. When  $I_2$  changes from 0 to 1, Z becomes 0. Otherwise, Z is 0. Realize the circuit using J-K flip flop.

- 4. Attempt any two of the following :

- (a) Describe the differences between the following :

- (i) PLA and PAL

- (ii) Registered output PAL and GAL

Use logic diagrams for explanation.

## EEC302/VEQ-15048

- (b) Write short notes on the following :

- (i) Sequential and Random Access memories.

- (ii) One and multi-dimensional selection arrangement of memories.

- (c) Draw an ASM chart for a modulo-6 counter with a reset input.

- 5. Attempt any two of the following :

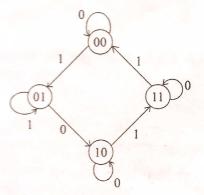

- (a) For the state diagram shown in figure, obtain the state table and design the circuit using minimum number of J-K FFs.

- (b) Differentiate synchronous and asynchronous sequential circuits. Explain the problem in asynchronous circuits.

- (c) What are the different types of hazards in asynchronous circuits ? Differentiate static-0 and static-1 hazards with waveform.